The rise of generative artificial intelligence is not limited to content creation and chatbots—it is now firmly entering the fabric of microelectronics design. In 2025, design automation tools have begun to use AI models to propose transistor layouts, optimize routing, and suggest architectural tradeoffs, dramatically accelerating chip development cycles. This shift is fundamentally altering how chips are conceived, verified, and produced.

Traditionally, electronic design automation (EDA) has been a heavily human‑driven, iterative process requiring expert engineers to balance power, performance, area, and thermal constraints across many layers and interconnects. But now, tools from prominent EDA vendors are embedding generative AI modules that can propose floorplans, place standard cells, and refine critical path timing more intelligently. For example, a designer might specify throughput targets, power budgets, and die area, and the AI‑assisted tool would generate candidate layouts, simulate performance, and suggest optimizations—all within a fraction of the time manual methods required.

This AI‑driven optimization is especially powerful in domains like analog design, where small parasitic interactions or feedback loops often require human intuition. Emerging systems can analyze layout sensitivity, recommend guard rings, or detect mismatches by referencing large datasets of prior designs. In effect, they’re becoming “assistant designers” that augment human expertise rather than replace it.

Another area where AI is making headway is in yield prediction and defect mitigation. By training models on prior wafer data, test results, and process logs, AI systems can forecast defect hotspots, propose redundant functional units, or preemptively reconfigure metal layers to avoid known weaknesses. This proactive approach reduces catastrophic failures and shortens post-silicon repair cycles.

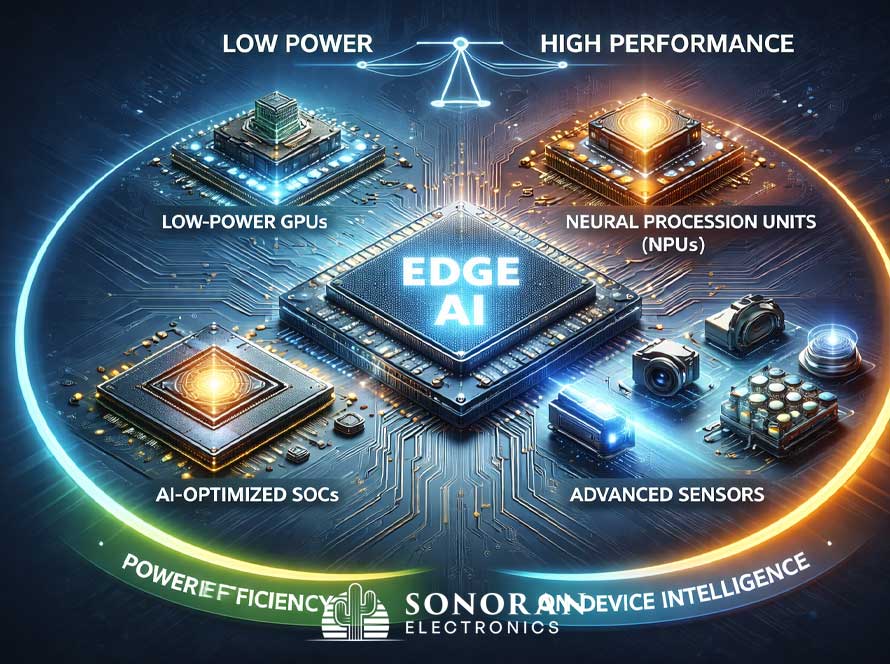

Furthermore, AI is streamlining collaboration between software, hardware, and system teams. Generative models can intake high‑level algorithmic descriptions—such as neural network topologies—and automatically translate them into optimized accelerator blocks, memory hierarchies, and interface logic. The result is a more cohesive co‑design pipeline where architectural choices and microelectronic constraints inform each other in a feedback loop.

However, there are challenges. Because AI models themselves can make “creative” suggestions, verifying their correctness, safety margins, and adherence to design rules remains critical. EDA vendors must ensure that AI proposals meet industry validation standards. Also, the training data used must be carefully curated to prevent overfitting or propagation of suboptimal design practices.

From a business perspective, the introduction of generative EDA shortens time to market and reduces human bottlenecks. In an era where startup chip companies and edge‑AI firms need rapid iteration, having design tools that internalize best practices and scale with project complexity is a competitive advantage.

As the lines blur between human designers and AI co‑designers, the future of microelectronics is becoming increasingly symbiotic. Automation powered by generative AI is not merely a productivity boost—it’s enabling design innovation at complexity levels previously considered unattainable.